Sign up to save your library

With an OverDrive account, you can save your favorite libraries for at-a-glance information about availability. Find out more about OverDrive accounts.

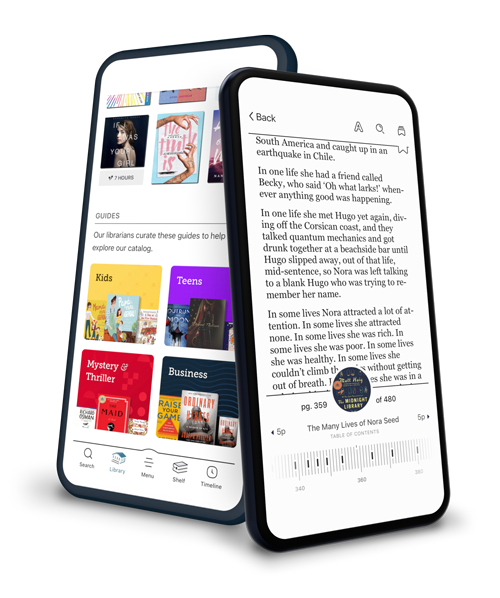

Find this title in Libby, the library reading app by OverDrive.

Search for a digital library with this title

Title found at these libraries:

| Loading... |

Scalable Hardware Verification with Symbolic Simulation presents recent advancements in symbolic simulation-based solutions which radically improve scalability. It overviews current verification techniques, both based on logic simulation and formal verification methods, and unveils the inner workings of symbolic simulation. The core of this book focuses on new techniques that narrow the performance gap between the complexity of digital systems and the limited ability to verify them. In particular, it covers a range of solutions that exploit approximation and parametrization methods, including quasi-symbolic simulation, cycle-based symbolic simulation, and parameterizations based on disjoint-support decompositions.

In structuring this book, the author's hope was to provide interesting reading for a broad range of design automation readers. The first two chapters provide an overview of digital systems design and, in particular, verification. Chapter 3 reviews mainstream symbolic techniques in formal verification, dedicating most of its focus to symbolic simulation. The fourth chapter covers the necessary principles of parametric forms and disjoint-support decompositions. Chapters 5 and 6 focus on recent symbolic simulation techniques, and the final chapter addresses key topics needing further research.

Scalable Hardware Verification with Symbolic Simulation is for verification engineers and researchers in the design automation field.

Highlights: